Mail:info@anke-pcb.com

Whatapp/wechat: 008618589033832

Skype: Sannyduanbsp

Tatlong aspeto upang ma -secure ang integridad ng kuryente sapagdidisenyo ng PCB

Sa modernong elektronikong disenyo, ang integridad ng kuryente ay isang kailangang -kailangan na bahagi ng disenyo ng PCB. Upang matiyak ang matatag na operasyon at pagganap ng mga elektronikong aparato, dapat nating isaalang -alang at disenyo nang komprehensibo mula sa mapagkukunan ng kapangyarihan hanggang sa tatanggap.

Sa pamamagitan ng maingat na pagdidisenyo at pag -optimize ng mga module ng kuryente, mga panloob na eroplano ng layer, at mga power supply chips maaari nating tunay na makamit ang integridad ng kuryente. Ang artikulong ito ay susuriin sa mga tatlong pangunahing aspeto upang magbigay ng praktikal na gabay at mga diskarte para sa mga taga -disenyo ng PCB.

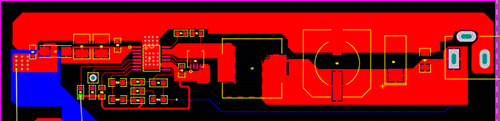

I. Mga kable ng layout ng module ng kuryente

Ang module ng kuryente ay ang mapagkukunan ng enerhiya ng bawat elektronikong aparato, ang pagganap at layout nito ay direktang nakakaapekto sa katatagan at kahusayan ng buong sistema. Ang tamang layout at pagruruta ay hindi lamang maaaring mabawasan ang pagkagambala sa ingay ngunit masiguro din ang makinis na kasalukuyang daloy, sa gayon ay mapapabuti ang pangkalahatang pagganap.

2. Layout ng Module ng Module

1. Pagproseso ng Source:

Ang module ng kuryente ay dapat bayaran ng espesyal na pansin dahil nagsisilbi itong panimulang punto ng kapangyarihan. Upang mabawasan ang pagpapakilala sa ingay, ang kapaligiran sa paligid ng module ng kuryente ay dapat na panatilihing malinis hangga't maaari upang maiwasan ang katabing sa ibaMataas na dalaso mga sangkap na sensitibo sa ingay.

2.Close sa power supply chip:

Ang module ng kuryente ay dapat mailagay nang malapit sa chip na ibinibigay ng kuryente hangga't maaari. Maaari itong mabawasan ang mga pagkalugi sa kasalukuyang proseso ng paghahatid at bawasan ang mga kinakailangan sa lugar ng panloob na eroplano ng layer.

3.Heat pagsasaalang -alang sa pagwawaldas:

Ang module ng kuryente ay maaaring makabuo ng init sa panahon ng operasyon, kaya dapat itong matiyak na walang mga hadlang sa itaas nito para sa pagwawaldas ng init. Kung kinakailangan, ang mga heatsinks o tagahanga ay maaaring maidagdag para sa paglamig.

4.Avoiding loops:

Kapag ang pag -ruta, iwasan ang pagbuo ng kasalukuyang mga loop upang mabawasan ang posibilidad ng pagkagambala ng electromagnetic.

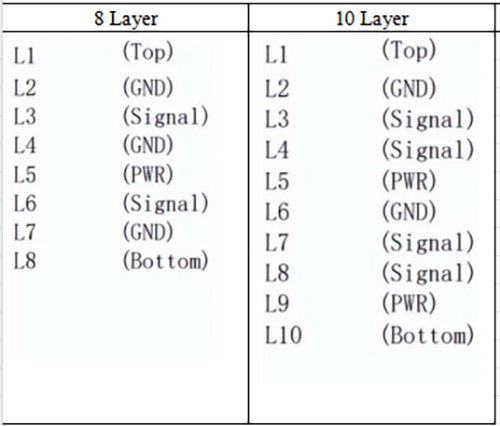

Ii. Panloob na Pagpaplano ng Disenyo ng Layer ng Layer

A. Disenyo ng Layer Stack

In Disenyo ng PCB EMC, Ang disenyo ng layer stack ay isang pangunahing elemento na kailangang isaalang -alang ang pamamahagi ng ruta at kapangyarihan.

a. Upang matiyak ang mga mababang katangian ng impedance ng eroplano ng kuryente at pagsipsip ng ingay sa ingay sa lupa, ang distansya sa pagitan ng mga eroplano ng kapangyarihan at lupa ay hindi dapat lumampas sa 10mil, karaniwang inirerekomenda na mas mababa sa 5mil.

b. Kung ang isang solong eroplano ng kuryente ay hindi maipatupad, ang isang layer ng ibabaw ay maaaring magamit upang mailabas ang eroplano ng kuryente. Ang malapit na katabing kapangyarihan at mga eroplano ng lupa ay bumubuo ng isang kapasitor ng eroplano na may minimum na impedance ng AC at mahusay na mga katangian ng mataas na dalas.

c. Iwasan ang katabing dalawang mga layer ng kuryente, lalo na sa mga malalaking pagkakaiba -iba ng boltahe, upang maiwasan ang pagkabit ng ingay. Kung hindi maiiwasan, dagdagan ang puwang sa pagitan ng dalawang mga layer ng kuryente hangga't maaari.

d. Ang mga eroplano na sanggunian, lalo na ang mga eroplano ng sanggunian ng kuryente, ay dapat mapanatili ang mga mababang katangian ng impedance at maaaring mai -optimize sa pamamagitan ng mga bypass capacitor at pagsasaayos ng layer.

B.Multiple Power Segmentation

a. Para sa mga tiyak na maliit na saklaw na mapagkukunan ng kuryente, tulad ng pangunahing boltahe na nagtatrabaho ng isang tiyak na chip ng IC, ang tanso ay dapat na inilatag sa layer ng signal upang matiyak ang integridad ng eroplano ng kuryente, ngunit maiwasan ang pagtula ng tanso na tanso sa layer ng ibabaw upang mabawasan ang radiation ng ingay.

b. Ang pagpili ng lapad ng segment ay dapat na angkop. Kapag ang boltahe ay mas malaki kaysa sa 12V, ang lapad ay maaaring 20-30mil; Kung hindi man, pumili ng 12-20mil. Ang lapad ng segmentasyon sa pagitan ng mga mapagkukunan ng analog at digital na kapangyarihan ay kailangang madagdagan upang maiwasan ang digital na kapangyarihan mula sa nakakasagabal sa kapangyarihan ng analog.

c. Ang mga simpleng network ng kuryente ay dapat makumpleto sa layer ng ruta, at ang mas mahabang mga network ng kuryente ay dapat na idinagdag ang mga capacitor ng filter.

d. Ang naka -segment na eroplano ng kapangyarihan ay dapat na panatilihing regular upang maiwasan ang hindi regular na mga hugis na nagdudulot ng resonance at nadagdagan ang impedance ng kuryente. Ang mahaba at makitid na mga piraso at mga dibisyon na hugis ng dumbbell ay hindi pinapayagan.

C.Plane Filter

a. Ang eroplano ng kuryente ay dapat na malapit na isinama sa eroplano ng lupa.

b. Para sa mga chips na may mga frequency ng operating na higit sa 500MHz, lalo na umaasa sa pag -filter ng eroplano ng eroplano at gumamit ng isang kumbinasyon ng pag -filter ng kapasitor. Ang epekto ng pag -filter ay kailangang kumpirmahin ng simulation ng integridad ng kuryente.

c. I -install ang mga inductors para sa mga decoupling capacitor sa control eroplano, tulad ng pagpapalawak ng capacitor lead at pagtaas ng mga kapasitor na vias, upang matiyak na ang impedance ng power ground ay mas mababa kaysa sa target na impedance.

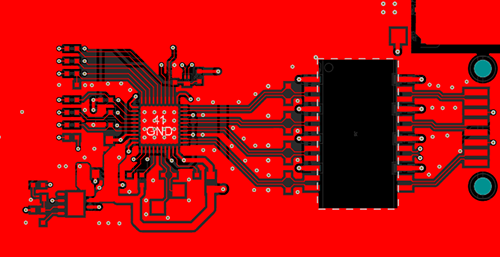

III. Mga kable ng layout ng power chip

Ang power chip ay ang pangunahing bahagi ng mga elektronikong aparato, at tinitiyak ang integridad ng kapangyarihan nito ay mahalaga para sa pagpapabuti ng pagganap at katatagan ng aparato. Ang kontrol ng integridad ng kuryente para sa mga power chips ay pangunahing nagsasangkot ng pag -ruta ng paghawak ng mga chip power pin at tamang layout at mga kable ng mga decoupling capacitor. Ang sumusunod ay detalyado ang mga pagsasaalang -alang at praktikal na payo tungkol sa mga aspeto na ito.

A.CHIP POWER pin ruta

Ang pagruruta ng mga pin ng chip power ay isang mahalagang bahagi ng kontrol ng integridad ng kuryente. Upang magbigay ng isang matatag na kasalukuyang supply, inirerekomenda na palalimin ang pagruruta ng mga pin ng kapangyarihan, sa pangkalahatan sa parehong lapad ng mga pin ng chip. Karaniwan, angMinimum na lapadHindi dapat mas mababa sa 8mil, ngunit para sa mas mahusay na mga resulta, subukang makamit ang isang lapad ng 10mil. Sa pamamagitan ng pagtaas ng lapad ng ruta, maaaring mabawasan ang impedance, sa gayon binabawasan ang ingay ng kuryente at tinitiyak ang sapat na kasalukuyang supply sa chip.

B.Layout at ruta ng mga decoupling capacitor

Ang mga capacitor ng decoupling ay may mahalagang papel sa kontrol ng integridad ng kuryente para sa mga power chips. Depende sa mga katangian ng kapasitor at mga kinakailangan sa aplikasyon, ang mga decoupling capacitor ay karaniwang nahahati sa malaki at maliit na capacitor.

a. Malaking capacitor: Ang mga malalaking capacitor ay karaniwang pantay na ipinamamahagi sa paligid ng chip. Dahil sa kanilang mas mababang dalas ng resonant at mas malaking radius ng pag-filter, maaari nilang epektibong i-filter ang ingay na mababa ang dalas at magbigay ng matatag na supply ng kuryente.

b. Mga maliliit na capacitor: Ang mga maliliit na capacitor ay may mas mataas na dalas ng resonant at mas maliit na pag -filter ng radius, kaya dapat silang mailagay nang malapit hangga't maaari sa mga pin ng chip. Ang paglalagay ng mga ito ay masyadong malayo ay maaaring hindi epektibong i-filter ang mataas na dalas na ingay, nawawala ang decoupling effect. Tinitiyak ng tamang layout na ang pagiging epektibo ng mga maliliit na capacitor sa pag-filter ng high-frequency na ingay ay ganap na ginagamit.

C.Wiring Paraan ng Parallel Decoupling Capacitor

Upang higit pang mapagbuti ang integridad ng kapangyarihan, ang maraming mga capacitor ng decoupling ay madalas na konektado sa kahanay. Ang pangunahing layunin ng pagsasanay na ito ay upang mabawasan ang katumbas na serye ng inductance (ESL) ng mga indibidwal na capacitor sa pamamagitan ng magkatulad na koneksyon.

Kapag kahanay ng maramihang mga capacitor ng decoupling, ang pansin ay dapat bayaran sa paglalagay ng mga vias para sa mga capacitor. Ang isang karaniwang kasanayan ay upang mai -offset ang mga vias ng kapangyarihan at lupa. Ang pangunahing layunin nito ay upang mabawasan ang mutual inductance sa pagitan ng mga decoupling capacitor. Tiyakin na ang mutual inductance ay mas maliit kaysa sa ESL ng isang solong kapasitor, upang ang pangkalahatang impedance ng ESL pagkatapos ng kahanay ng maramihang mga capacitor ng decoupling ay 1/N. Sa pamamagitan ng pagbabawas ng mutual inductance, ang kahusayan sa pag -filter ay maaaring epektibong mapahusay, tinitiyak ang pinahusay na katatagan ng kuryente.

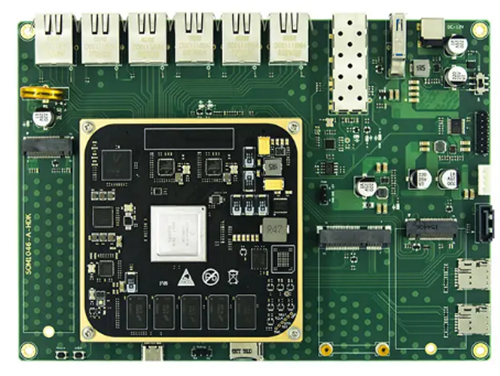

Layoutat pagruruta ng mga module ng kuryente, pagpaplano ng disenyo ng eroplano ng panloob na layer, at tamang paghawak ng layout ng power chip at mga kable ay kailangang -kailangan sa disenyo ng elektronikong aparato. Sa pamamagitan ng wastong layout at pagruruta, masisiguro natin ang katatagan at kahusayan ng mga module ng kuryente, bawasan ang pagkagambala sa ingay, at pagbutihin ang pangkalahatang pagganap. Ang disenyo ng stack ng layer at maraming segmentasyon ng kuryente ay higit na mai -optimize ang mga katangian ng mga eroplano ng kuryente, pagbabawas ng panghihimasok sa ingay ng lakas. Ang wastong paghawak ng layout ng power chip at mga kable at pagkabulok ng mga capacitor ay mahalaga para sa kontrol ng integridad ng kuryente, tinitiyak ang isang matatag na kasalukuyang supply at epektibong pag -filter ng ingay, pagpapahusay ng pagganap at katatagan ng aparato.

Sa praktikal na pagtatrabaho, ang iba't ibang mga kadahilanan tulad ng kasalukuyang magnitude, lapad ng ruta, bilang ng mga vias, mga epekto ng pagkabit, atbp. Sundin ang mga pagtutukoy ng disenyo at pinakamahusay na kasanayan upang matiyak ang kontrol at pag -optimize ng integridad ng kuryente. Sa ganitong paraan maaari tayong magbigay ng matatag at mahusay na supply ng kuryente para sa mga elektronikong aparato, matugunan ang pagtaas ng mga hinihingi sa pagganap, at itaboy ang pag -unlad at pag -unlad ng elektronikong teknolohiya.

Shenzhen Anke PCB Co, Ltd

Oras ng Mag-post: Mar-25-2024